Eugenio Villar – University of Cantabria

### FORMALIZATION OF THE MARTE/SYSTEMC INTEROPERABILITY FOR HW/SW CO-DESIGN

CopyRight by

2010-5-4

### Context

- SystemC

- Wide use for system modeling

- Increasing interest for system specification

- Untimed modeling > 25%

- Increasing interest in MARTE

- Increasing interest in MARTE/SystemC interoperability

#### Context

### Agenda

- Motivation

- Formalization of the Saturn design methodology

- MARTE/SystemC interoperability formalization

- Conclusions

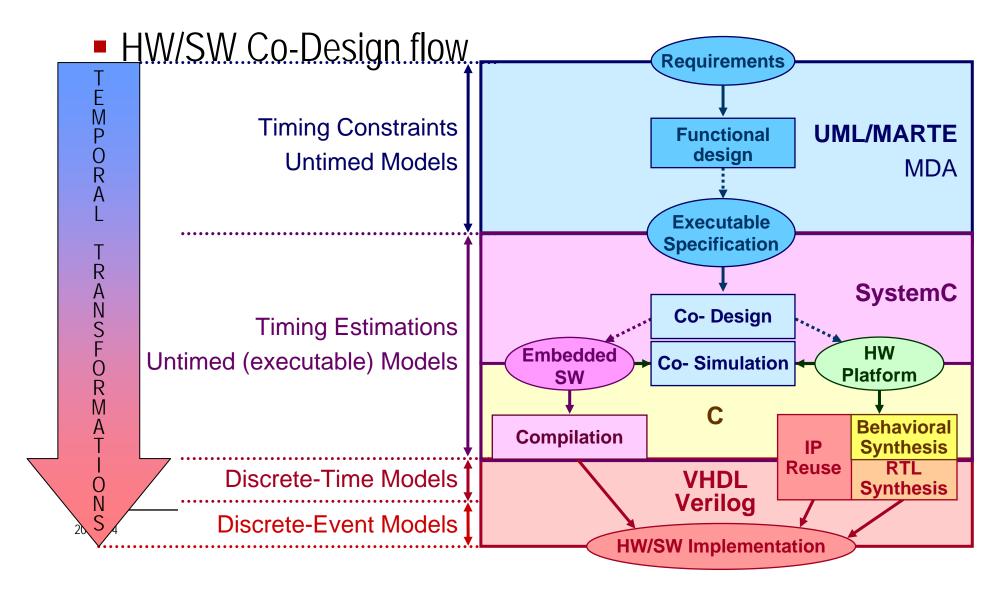

- Mature HW design process

- RTL description

- RTL simulation (Discrete-Time MoC)

- RTL synthesis

- Logic simulation (Discrete-Event MoC)

- Placement & Routing

- Static Timing Analysis

- Back-annotated logic simulation (Discrete-Event MoC)

- The MPSoC

- Multi-processing platform

- With 'some' additional HW

- Most of the functionality implemented as Embedded SW

Software Reliability

WASHINGTON (COMPUTERWORLD) - Software bugs are costing the U.S. economy an estimated \$59.5 billion each year, with more than half of the cost borne by end users and the remainder by developers and vendors, according to a new federal study.

Improvements in testing could reduce this cost by about a third, or \$22.5 billion, but it won't eliminate all software errors, the study said. Of the total \$59.5 billion cost, users incurred 64% of the cost and developers 36%.

- http://www.cse.lehigh.edu/~gtan/bug/softwarebug.html

- http://www.sereferences.com/software-failure-list.php

- http://www5.in.tum.de/~huckle/bugse.html ...

- Clear need for sound HW/SW design methods

- Formal methods in HW/SW System Engineering

- Formalization of the HW/SW Co-Design process

- Formalization of the MoCs at each level

- Horizontal heterogeneity

- Formalization of the transformations among MoCs

- Vertical heterogeneity

# **Objective**

- Formalization of the MARTE/SystemC interoperability

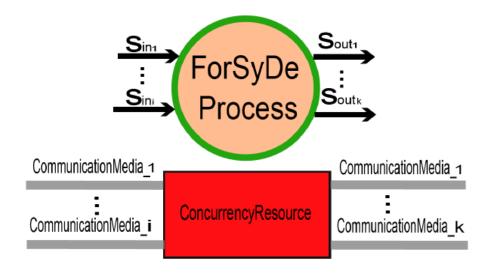

- ForSyDe as formal framework

- Untimed, Synchronous, Timed and Continuous MoCs

- Unified modeling

- Functionality

- Timing

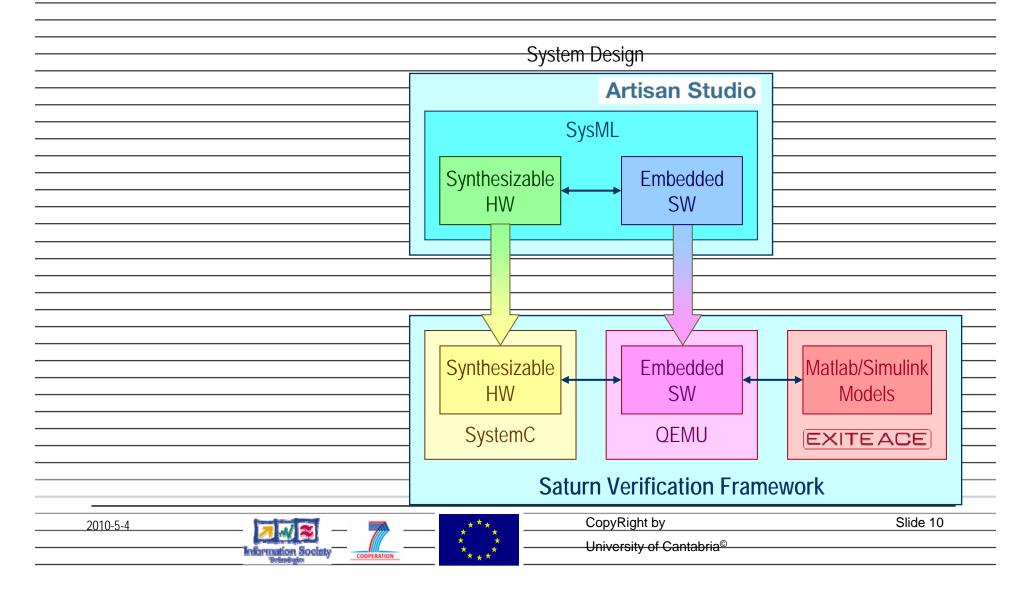

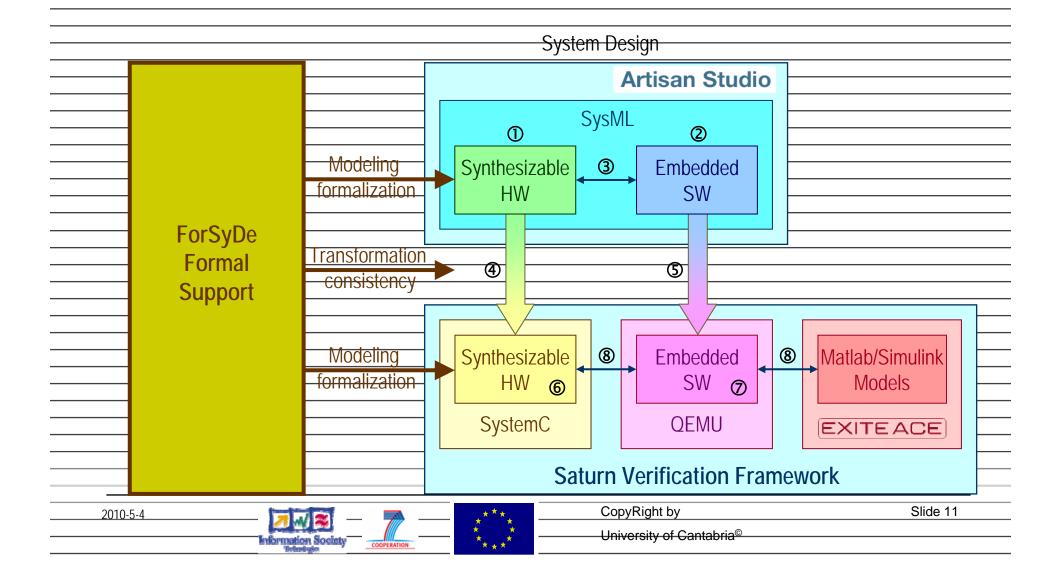

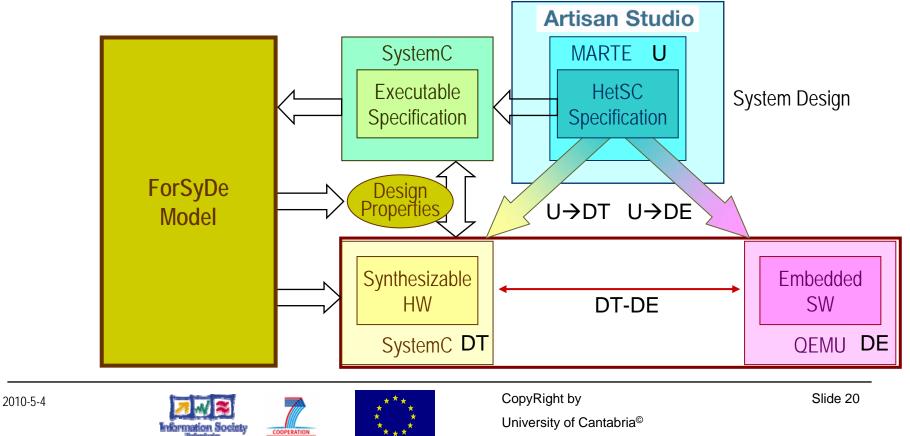

### The Saturn design methodology

THALES

UNIVERSIDAD

UNIVERSITÄT PADERBORN

## The ForSyDe Formal Support

THALES

UNIVERSIDAD

UNIVERSITÄT PADERBORN

### The ForSyDe Formal Support

SystemC/RTL synthesizable code

🗖 atego

## The ForSyDe Formal Support

CopyRight by University of Cantabria<sup>©</sup>

THALES INTRACOM

## The ForSyDe Formal Support

TELECOM

atego

atego

# <u>J</u>

# The ForSyDe Formal Support

## The ForSyDe Formal Support

INTRACOM

TELECOM

HW/SW co-simulation

atego

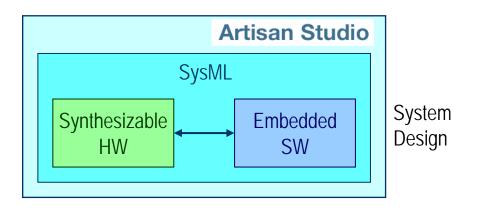

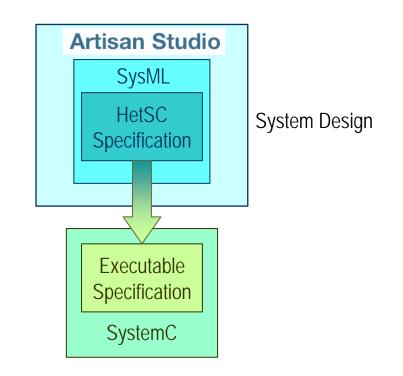

## Extension of the Saturn SysML profile

- System-level specification capabilities

- System-level modeling

atego

Reference to any HW/SW implementation

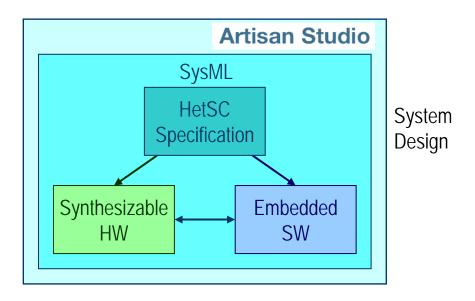

# Extension of the Saturn SysML profile

- System-level specification capabilities

- System-level modeling

- HetSC profile

atego

# Extension of the Saturn SysML profile

SystemC HetSC generation

CopyRight by University of Cantabria<sup>©</sup>

2010-5-4

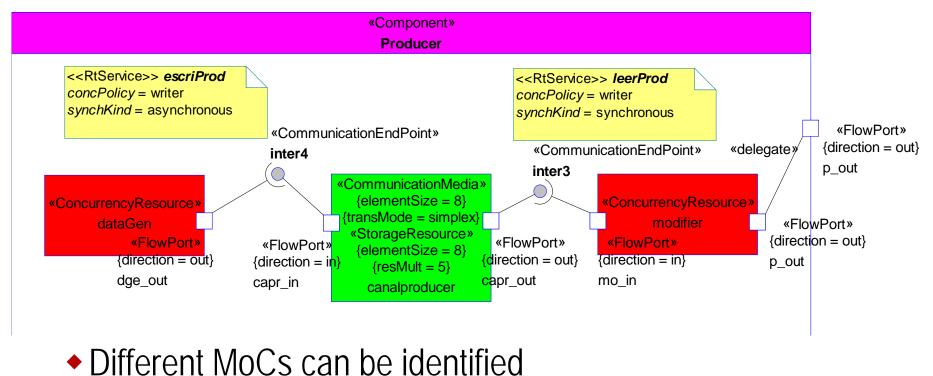

- MARTE computation and communication stereotypes

- Generic Resource Modeling

- MARTE computation and communication stereotypes

- Generic Resource Modeling

CopyRight by

- MARTE computation and communication stereotypes

- Generic Resource Modeling

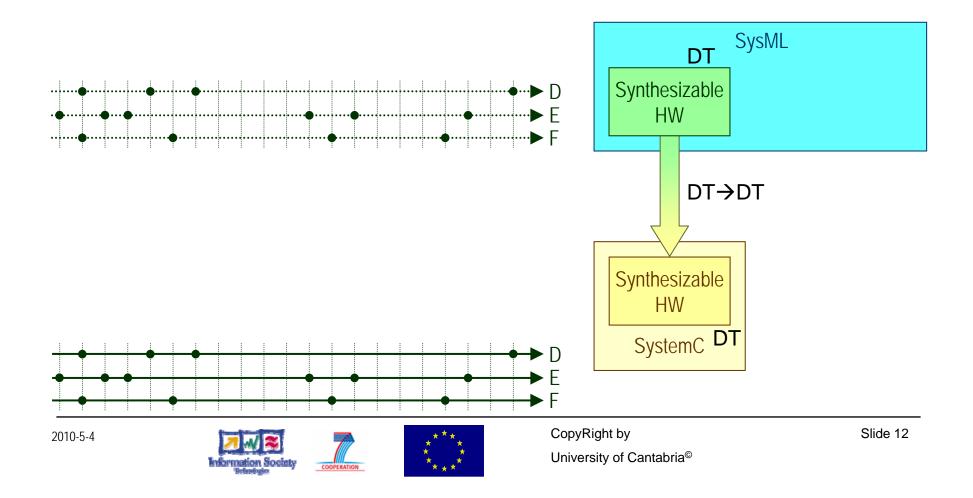

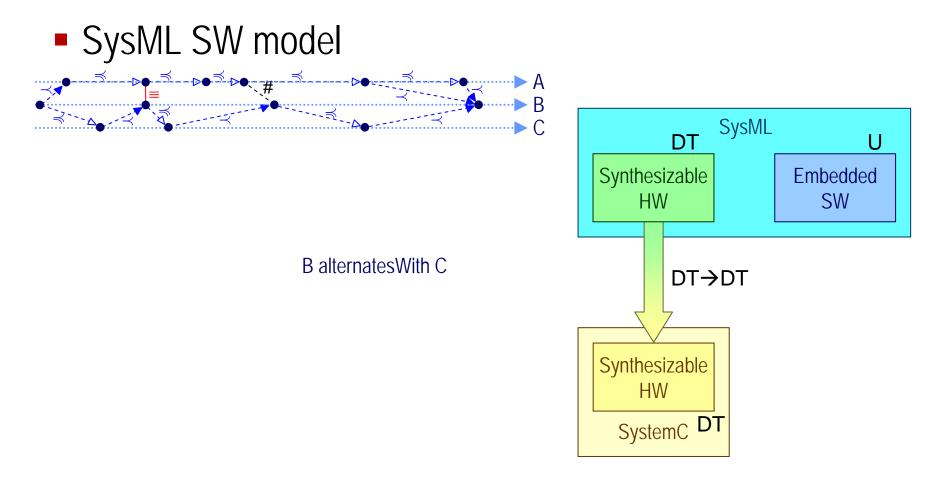

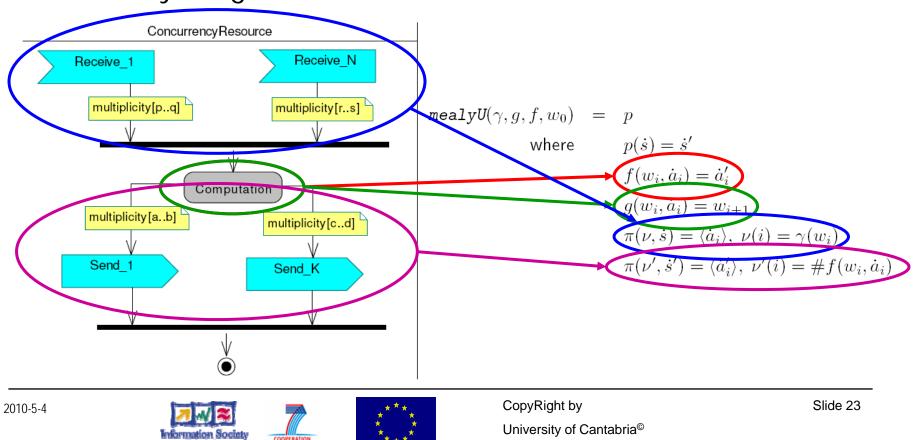

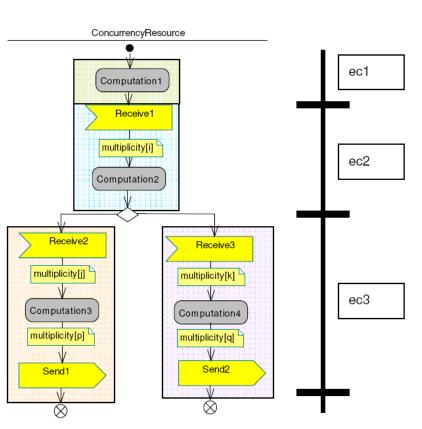

## MARTE/SystemC interoperability formalization

- MARTE computation

- Activity Diagrams

- MARTE computation

- Activation Cycles

Information Society COOPERAtion

CopyRight by University of Cantabria<sup>©</sup>

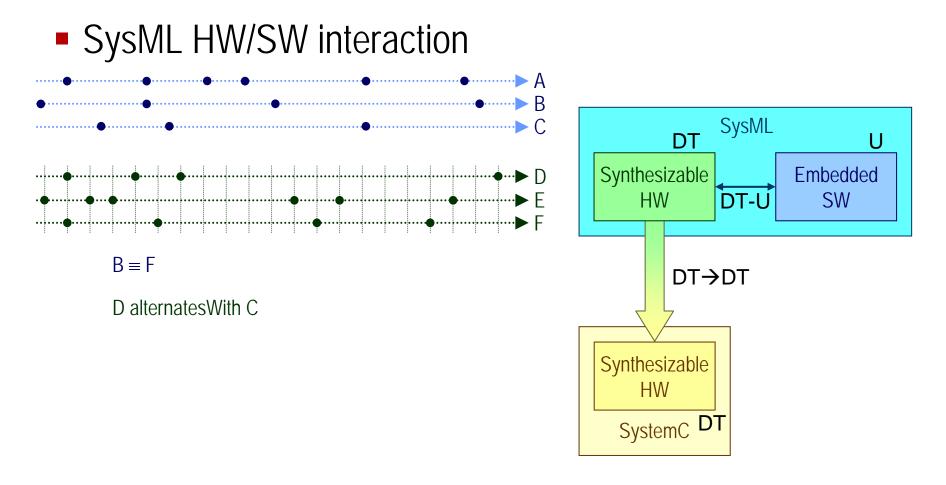

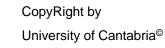

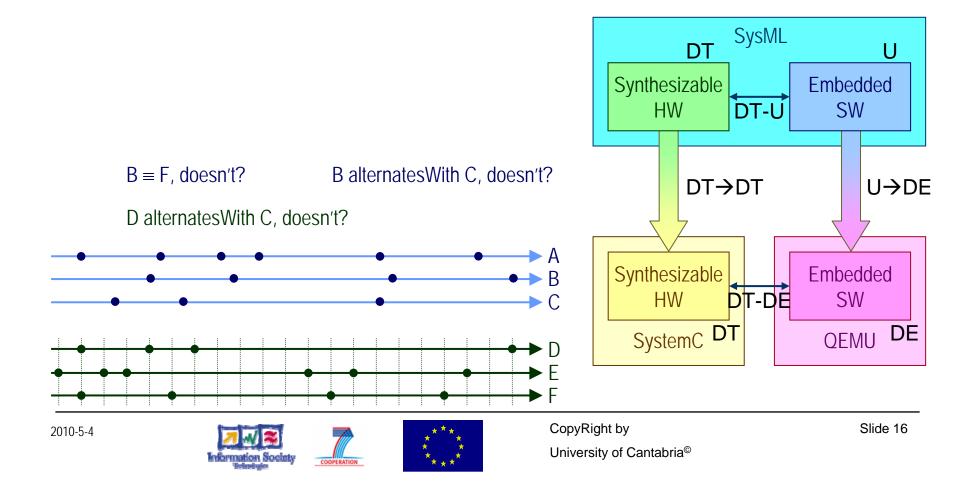

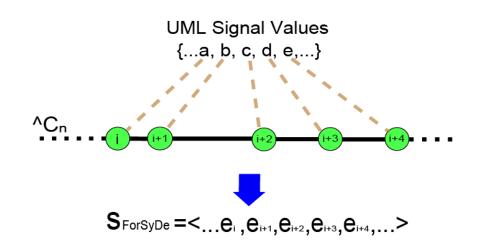

- MARTE timing

- UML signals and MARTE clocks as ForSyDe signals

- Clock relations

- Clock Constraints Specification Language

- Verification of design constraints

- MARTE clock relations

| $B \equiv F$                                                                  | D alternatesWith C                                                                                          |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| psl property B_synchonous_F is always<br>(B.write_CALL() and F.write_CALL()); | psl property D_alternates_C is always<br>(D.write_CALL() -><br>next(C.write_CALL() before D.write_CALL())); |

| psl assert B_synch_F;                                                         | psl assert D_alternates_C;                                                                                  |

SystemC assertions

CopyRight by University of Cantabria<sup>©</sup>

atego

- ForSyDe as formalization metamodel for Saturn

- Providing a formal framework

- Defining design rules and constraints

- HetSC extension to the Saturn profile

- MARTE/SystemC interoperability formalization

- First step towards a SystemC generation methodology

- Based on a formal framework

- Predictable executable specification results

- Application to system design verification